全球3纳米里程碑!三星抢发量产芯片,弯道超车台积电?

昨天,世界著名的半导体巨头三星,宣布了一条大新闻。基于3纳米(nm)制程的芯片,正式量产了!在纸面参数上,可谓是实现了质的飞跃——性能猛提30%,功耗猛降50%,面积也减少了35%。

来源:新智元

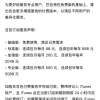

中间三位大咖抱的可不是普通的“盘子”,而是刚从三星华城电子园区生产线上拿下来的3纳米晶圆。

再看看周围的其他团队成员,笑得也相当开心。而且他们比的不是剪刀手,而是代表着3纳米的“3”。

性能拉满,能耗暴降

说起这个首次实现量产的3纳米芯片,就不得不提到它背后的MBCFET技术。

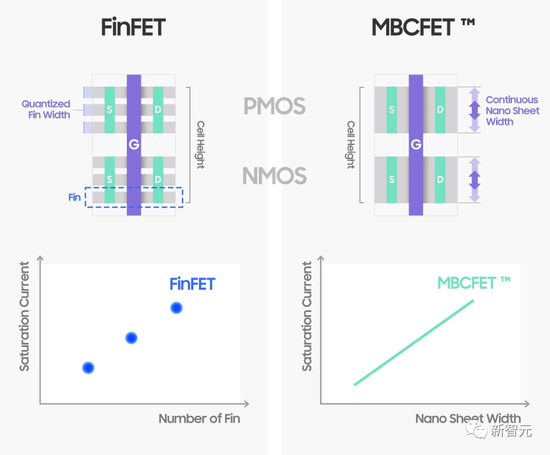

MBCFE突破了此前FinFET的性能限制,通过降低电源电压水平来提高功率效率,同时还通过增加驱动电流能力提高了性能。

说起纳米片晶体管和半导体芯片的应用,三星这还是第一次。目的是为了实现高性能、低功耗的计算服务。最终能在移动处理器上也得以应用。

三星的总裁,兼代工业务负责人Siyoung Choi博士表示,“我们一直都发展得很快。三星一直紧跟前沿的技术,然后想办法把它们投入生产应用。比如说之前的首个High-K金属栅极、FinFET,还有EUV等等。”

“现在,我们又是第一个研究MBCFET的。”

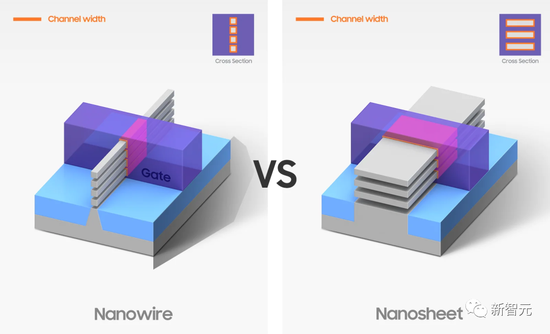

三星的独家技术应用了有更宽的通道的纳米片,和用通道窄一点的纳米线的传统GAA技术相比,不光提升了性能,还提高了能源利用率。

不仅如此,应用了3纳米GAA技术,三星还能通过调整纳米片的通道宽度,优化功耗和性能,来满足各类客户的不同需求。

此外,3纳米GAA的设计非常灵活,简直就是为设计技术协同优化(DTCO)量身打造的。我们主要看新技术应用以后,芯片的功耗、性能和面积大小(PPA,Power、Performance、Area)三个维度来量化。

和5纳米的工艺相比,第一代3纳米工艺相比5纳米降低了高达45%的能耗,提升了23%的性能,减少了16%的面积。

光是一代的提升就已经肉眼可见了。

更不用说二代的PPA——功耗降低50%、性能提高30%、面积减少35%,比一代又优秀了不知多少。

良品率行不行?量产靠谱吗?

在外行眼里,能量产3纳米的工艺可能已经不敢想象了,但是也有分析师表达了其它的一些看法。

来自大和资本市场的SK Kim表示,“三星能干成这件事,确实有意义。但还远远不够。量产只是第一步,你在能用它来生产主流芯片之前,比如手机CPU这种,不见得能多挣多少钱。”

这其实是有根据的。

4月份就有消息传出来,说三星基于GAA的3纳米工艺良率才在10%~20%之间,比预期低得多。

三星需要付出更多的精力和成本来解决这个问题。

5月份就再次传出了3纳米良率问题已得到解决的消息,6月初才又传出来进入试验性量产的说法。

不过,有了4月的前车之鉴,业界很多专家都对三星3纳米的真实情况打了个小小的问号。

据报道,6月22日,市场再次传出了三星3纳米芯片量产再一次推迟的消息,还是因为良率问题。

而且,三星之前给别的大厂代工芯片还闹出过不少笑话。

最逗的可能就是当时超级出圈的骁龙888,人送外号“大火龙”。

(图:大火龙真身)

当时高通找到三星来代工生产这款芯片的时候,没想到三星这么能搞。虽然当时都是5纳米工艺,但是三星和台积电的5纳米可差得太多了。

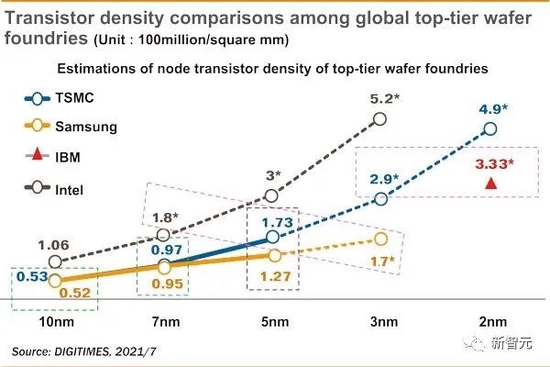

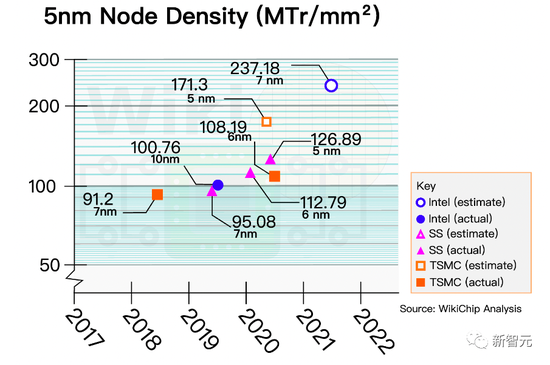

数据显示,三星5纳米的晶体管密度每平方毫米只有127万个晶体管,而台积电达到了173万个。差了46%。

说来好笑,“大火龙”用起来热的把CPU都烧的虚焊了。

可见,抛开别的不谈,三星在芯片制作这方面,总感觉差点意思。

但不管怎么说,就3纳米工艺而言,技术归技术,该先进还是先进。

抛弃FinFET,首次采用GAA技术

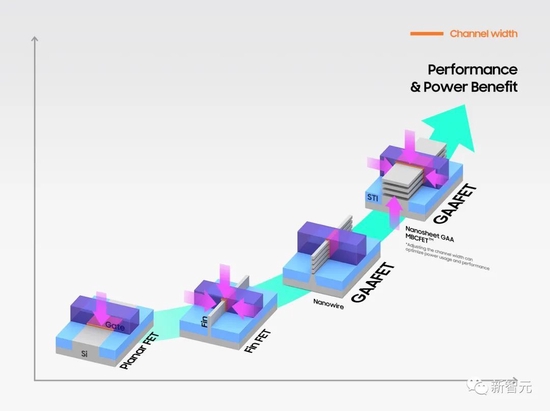

相比于传统芯片采用的“FinFET”技术而言,三星采用的“GAAFET”技术明显占据优势。

“FinFET”技术已经在芯片上使用了将近10年时间,它帮助芯片完成了从28纳米工艺到5纳米工艺的跨越。

相比之下,“GAAFET”的沟道被栅极四面包围,沟道电流比三面包裹的“FinFET”更加顺畅,这样的设计进一步改善了对电流的控制,从而优化栅极长度的微缩。不仅消耗功率低,耗电量低,速度也更快了。

三星认为采用纳米线沟道设计必须堆叠更多的线层以增加总沟道宽度,这样的工艺不仅复杂,且付出的成本可能也大于收益。

因此,三星设计了一种全新的GAA形式——MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),采用多层堆叠的纳米片(Nanosheet)来替代“GAAFET”中的纳米线(Nanowire)。

“MBCFET”采用了具有更大宽度的片状结构,同时保留了所有“GAAFET”优点,实现了最小化复杂度。

基于纳米片的“MBCFET”具有极高的可定制性,纳米片的宽度是定义功率和性能特性的关键指标,即纳米片的宽度越大,它的性能就越高。

因此,专注于低功耗的晶体管设计可以使用更小的纳米片,而需要更高性能则可以使用更宽的纳米片。

现在我们再来看一下此时的台积电老大哥有什么进展。

台积电在3纳米制程工艺上并没有选择GAA架构的晶体管,而是依然采用“FinFET”,通过复用之前成熟稳定的技术,这会为台积电的产品带来更好的稳定性,同时也能更好的控制成本,使利益最大化。

最关键的是,这样的操作可以给台积电争取更多时间实现对GAA晶体管架构的优化。

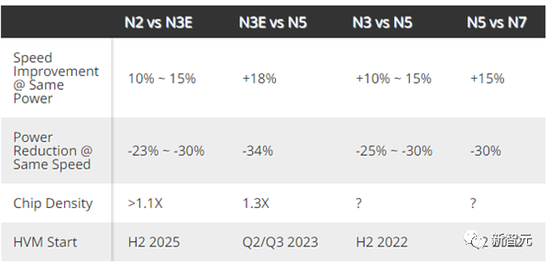

根据台积电此前“2022年台积电技术论坛”上公布的数据显示,其依然采用FinFET晶体管架构的3纳米的制程工艺,相比前代的5纳米制程工艺,性能将提升18%,功耗可降低34%,晶体管密度可提升30%。

从表中也可以看出,台积电的2纳米制程的部分技术指标:相较于3纳米的低成本版工艺,在相同功耗下,台积电2纳米工艺的性能将提升10~15%;而在相同性能下,台积电2纳米工艺的功耗将降低23~30%;晶体管密度仅提升了10%。

得此提升的原因主要是,在晶体管架构方面,台积电N2抛弃了“FinFET”,采用了全新的纳米片晶体管架构,即台积电版的“GAAFET”。

去年,Digitimes表明,三星3nm工艺可达成的晶体管密度大约为170 MTr/mm²(百万晶体管每平方毫米);而台积电早在5nm时代就已经将晶体管密度推进到了173 MTr/mm²。

另外Wikichip去年年中预测:台积电3nm工艺的晶体管密度可以达到291.21 MTr/mm²,在Digitimes的这张表里看起来也差不多。

如果三星3nm工艺真的只有表中170 MTr/mm²的程度,那么这和台积电的差距,就一目了然了!

最终,台积电的3纳米到底会带来多强烈的“震撼”,我们拭目以待!

热门评论

>>共有0条评论,显示0条