英特尔先进封装蓝图:单封装整合16颗计算芯片与24颗HBM5高带宽内存

英特尔代工业务近日发布一段展示先进封装技术的短片,提出通过Foveros 3D与EMIB-T互连,将芯粒规模扩展到传统光刻视场面积(约830平方毫米)12倍的宏大构想。根据介绍,这一方案可在单一封装内容纳多达16颗计算芯片,并搭配24颗HBM5高带宽内存模块,面向未来超大规模算力需求。

在该设计中,基础芯片(base die)采用18A-PT制程制造,并引入背面供电(backside power delivery)以提升逻辑密度与可靠性,同时在其上集成类似“Clearwater Forest”架构的SRAM结构。这些基础芯片为上层计算芯粒提供“地基”,而计算芯粒将使用更先进的14A或14A-E节点打造,具备第二代RibbonFET晶体管以及PowerDirect等新一代供电技术。

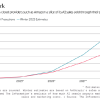

Foveros Direct 3D互连通过超细间距混合键合实现垂直堆叠,而EMIB-T则在封装内部采用穿硅通孔(TSV),在多个芯粒间提供更高带宽的互联能力。这种组合不仅突破了单一光刻视场的尺寸限制,还被规划为同时兼容HBM4、HBM5以及未来版本的HBM高带宽内存标准,以满足AI加速、HPC等领域对带宽和容量不断提升的需求。

随着先进封装技术的演进,英特尔还描绘了功耗高达5000 W的GPU设计蓝图,并计划通过集成式电压调节器(IVR)以及Foveros-B等封装方案,在2027年前后将此类超高功耗GPU推向现实。公司此前已经为现已停产的“Ponte Vecchio”加速卡打造过复杂封装形态,而即将登场的“Jaguar Shores”AI加速器也被视为这一技术路线的延续与升级。

为支撑上述路线,英特尔正持续扩充封装产能,例如其在马来西亚建设的Project Pelican封装厂已投产EMIB与Foveros封装能力,以服务自家与外部客户。随着更多芯片设计公司开始考虑采用英特尔的14A工艺与EMIB封装方案,英特尔在高端封装领域正被视为台积电CoWoS体系的有力竞争者之一。