身处后摩尔时代,半导体行业正面临着一场艰苦的“良率”战斗。随着芯片越来越复杂化,晶体管密度成倍增加,芯片制造良率管理难度也呈指数级增长,特别是对于那些追求先进制程的晶圆厂而言,更是会成为致命伤。

良率:半导体工厂的生命线

良率是半导体工厂的核心竞争力所在,也被称为是半导体工厂的“生命线”。

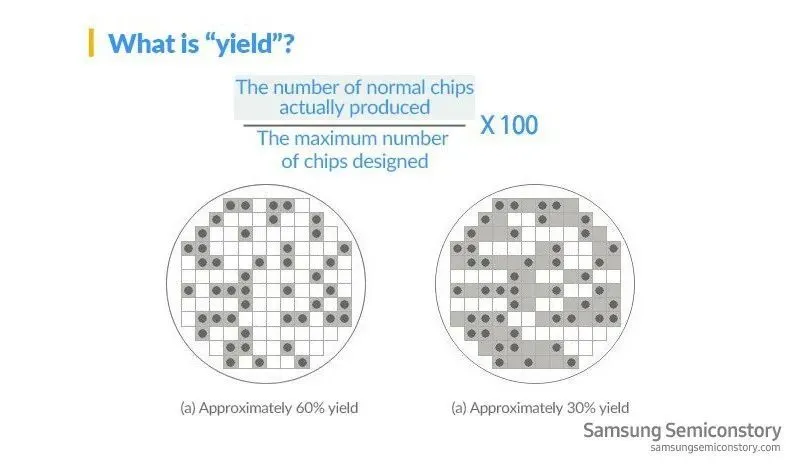

半导体良品率是实际生产的芯片总数与一个晶圆上最大芯片(集成电路)数的百分比,换句话说,良率是实际生产的数量与投入的总数量之比。良品率越高,生产率就越高,良率直接影响着成本和产能利用率。因此,提高良品率在半导体行业非常重要。同时,良率也是评估企业竞争力的重要标志之一,直接反映了制造过程的稳定性和产品质量的可靠性。

在逻辑芯片领域,按着摩尔定律的指引,目前能够实现量产的最先进工艺是3纳米。在该领域,台积电和三星是两大主要的玩家,两家在这场3nm之战中展开了激烈角逐。

三星于2022年6月率先宣布3nm量产,比台积电早几个月。三星是业界率先在3nm中引入栅极环绕 (GAA) 工艺的厂商,相比之下,台积电仍然采用FinFET晶体管架构。但是三星却在良率上遭遇了滑铁卢,虽然三星近日否认了韩媒ZDNet Korea所报道的,三星3nm良率低于20%的消息,然而由于良率问题,三星3nm确实流失了大量客户。

Google的Tensor处理器在第四代之前都委托给三星电子代工部门,但从引入 3nm 工艺的第五代开始,就转向了台积电。三星自家的Exynos 2500芯片也深受良率困扰,6月25日,知名分析师郭明錤在X(原Twitter)平台上发布社交动态评论,称由于三星自研的Exynos 2500处理器3纳米芯片良率低于预期而无法出货。

预计今年,包括智能手机、服务器、人工智能等在内的Fabless公司及IT大厂都将开始将3nm作为主要制程。在良率这个重要的考核指标面前,由于台积电的领先优势,预计将获得大部分大厂的3nm订单,这将有可能进一步拉大台积电与三星电子的市占率差距。

然而,即使是台积电,目前其3nm工艺的良率相较上一代也并不高。台积电目前也在积极提升3nm的良率。

良率低的问题不仅限于逻辑芯片领域,存储芯片也面临着同样的挑战。生成式AI正在消耗大量的HBM存储芯片,但是良率一直是NVIDIA GPU芯片大规模量产的拦路虎之一。据路透社报道,三星的高带宽存储HBM3芯片的生产良率约为10%~20%,而SK海力士的HBM3良率可达60%~70%。在传统的DRAM存储方面,三星第五代10纳米级(1b)制程DRAM的良率未达业界80%至90%的一般目标,迫使三星在上个月成立专门工作小组以解决这一问题。

而接下来,生成式AI还在滚滚向前,对芯片算力的需求望不到底。为了获得更高性能、更高算力的AI芯片:

一方面,逻辑厂商正在积极向2nm工艺突破,台积电和三星目前都计划在2025年开始2nm大规模量产,与此同时,还在发力FOPLP(扇出型面板级封装)等先进封装技术;

另一方面,存储厂商也在大力投入下一代HBM(即HBM4)的研发,各种先进的技术也在考虑当中,例如混合键合。

可想而知,届时良率又会成为一大难关。据《韩国经济日报报道》,SK海力士正在招聘数十名与HBM相关的职位,在其招聘启事中显示,希望寻找芯片专家能够通过改进代工工艺和测试逻辑芯片,进而提高HBM芯片的良率。

良率低是半导体厂商普遍面临的难题,也是制约芯片产业发展的瓶颈。从经济学角度上讲,提升芯片良率也可以视为摩尔定律的另一种延续。如何在新技术不断推陈出新的背景下,提高良率,成为每一家半导体厂商必须解决的关键问题。

良率提升,为何如此难?

想要提高良率,首先要明确导致良率低的原因有哪些?影响半导体制造良率的因素众多,但无外乎“人、机、料、法、环、测”。

具体而言:

人:操作人员的技术水平和操作规范性直接影响生产过程的稳定性

机:半导体制造设备的精度和稳定性直接影响芯片的微观结构和尺寸

料:原材料的纯度和一致性影响芯片的质量

法:工艺参数控制和操作精度对良率至关重要

环:生产车间的环境因素会影响芯片的制造过程

测:测试设备性能和测试方法影响良率评估的准确性

然而,随着芯片制程不断向先进制程迈进,影响良率的因素更是让人“难以捉摸”:

一方面,工艺的进步所涉及的工艺步骤和材料种类增多,芯片上的缺陷种类也越来越繁多,而且缺陷成因复杂,难以分析和排查。另一方面,新工艺、新材料、新设备的不断引入也给良率提升带来了新的挑战。此外,提升良率需要投入大量的资金和人力,包括研发投入、设备投入、人才培养等。而且一些先进的检测和分析手段也需要较高的成本。

这也是为何行业每往前迈进一个制程,良率都愈发难以提高。

为了提高良率,行业绞尽脑汁

为了提高半导体制造的良率,行业各方正不遗余力地进行多方面的优化和创新。

减少污染物:半导体的纷繁复杂的多个工艺步骤过程要用到大量的气体和溶液,作为半导体制造的“血液”,这些气/液体的纯度和可靠性在很大程度上决定着半导体器件的性能品质和良率。根据业内人士估计,污染造成的产量损失高达50%。

污染控制是半导体制造过程中至关重要的一环。如果气体和溶液中存在污染物,例如颗粒、杂质等,就会导致芯片出现缺陷,降低良率,甚至造成芯片报废。因此,如何有效去除这些污染物,确保“血液”的纯净,是半导体制造面临的重大挑战。

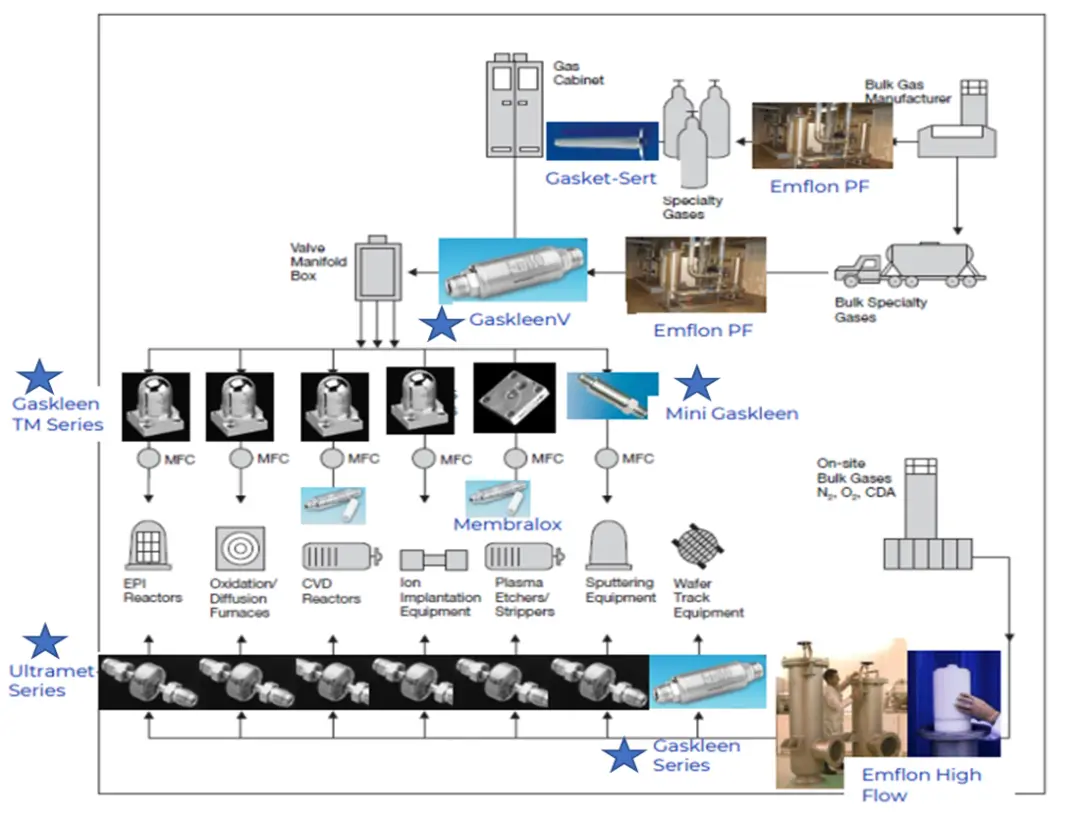

为了满足产业对先进工艺的迫切需求和对良率提升的挑战,全球过滤、分立和纯化解决方案的专家,颇尔公司(Pall corporation)近年来持续加大投资,去年,颇尔位于北京工厂的Gaskleen和Profile II双产线正式投产上市,今年6月份,颇尔又宣布新加坡工厂投产,新增了Litho光刻和WET湿法化学两条重要的过滤器产品线,可为当下先进工艺节点的逻辑和存储芯片制造提供强有力的支持。

颇尔北京气体过滤产品

颇尔能够提供全系列的半导体过滤器,涵盖CMP过滤器、光刻过滤器、气体过滤、气体纯化系统、超纯水过滤器、湿式蚀刻过滤器等等,这些强大的过滤器具有先进的纳米级杂质拦截功能,可在不同的关键工艺中清除颗粒、杂质等污染物,确保芯片的高品质和高良率。此外,高效的过滤技术可以减少污染物对设备的损害,延长设备的使用寿命,降低维护成本。

工艺优化:工艺优化是提高良率的基石。通过不断改进制程工艺,提高生产工艺的精度和可控性,减少缺陷的发生。例如,采用EUV光刻技术、3D封装/Chiplet/CoWos等各种先进封装技术等先进工艺。

引入AI和大数据分析技术:在半导体制造过程中,存在着大量的工艺参数和生产数据。借助AI、大数据等新兴技术实现更高的良率和更少的投入,已经成为行业共识。半导体工厂的数据管理向智能化升级是大势所趋。

工程智能(EI)、计算机集成制造(CIM)、制造执行系统(MES)等工业软件是半导体制造的重要工具。随着AI和大数据技术的融入,这些软件也在不断升级,为半导体工厂提供更加智能化的功能。在智能制造模式下,生产过程更加透明、可控,生产效率和产品质量得到显著提升。

自动化升级:减少人为操作环节,降低人为操作失误导致的缺陷率是提高良率的重要手段。自动引导车(AGV)、天车和自主移动机器人(AMR)的引入,正在加速半导体制造迈向智能制造的新时代。自动化设备的应用,可以有效减少人为操作环节,将工人从繁重的体力劳动和重复性工作中解放出来,从而降低人为操作失误导致的缺陷率,提高生产效率和产品质量。

由此可以看出,提高半导体制造良率是一项复杂的系统工程,需要半导体厂商从材料、工艺、设备、管理等多方面入手,不断创新和改进,才能有效降低缺陷率,提升产品竞争力。

结语

当今,良率提升成为半导体产业发展的核心驱动力之一。我们也看到像颇尔这样的过滤器厂商积极进取,扩产建厂,不断提升过滤技术的水平和产能,为先进工艺的应用和良率的提高保驾护航。

相信通过全产业链协作,持续攻坚克难,半导体行业一定能够不断提升良率水平,推动行业高质量发展,为全球经济增长贡献更大的力量。