AMD在下一代Zen 6处理器上计划引入全新的D2D互连技术,以取代现有的SERDES,目前这一技术变革已经在Strix Halo APU上初现端倪。AMD自Zen 2以来一直沿用SERDES PHY技术来实现CCD芯粒间的互连,但随着技术的进步和需求的增加,现有的互连方式已经逐渐显得力不从心。

SERDES代表串行器/解串器,主要用于将来自各个CCD的并行流量转换为串行比特流,并在芯片之间传输,随后解串器将串行数据流转换。

这就出现了两个缺点:串行化和解串行化过程需要能耗用于时钟恢复、均衡以及编码/解码;其次,数据流的转换增加了芯片间通信的延迟,这也是现有技术的一个主要缺点。

随着NPU等新功能的加入,AMD需要更稳定、低开销的带宽来连接内存和CCD,在Strix Halo APU中,AMD已经对进行了大改进,这可能预示着Zen 6处理器的未来发展方向。

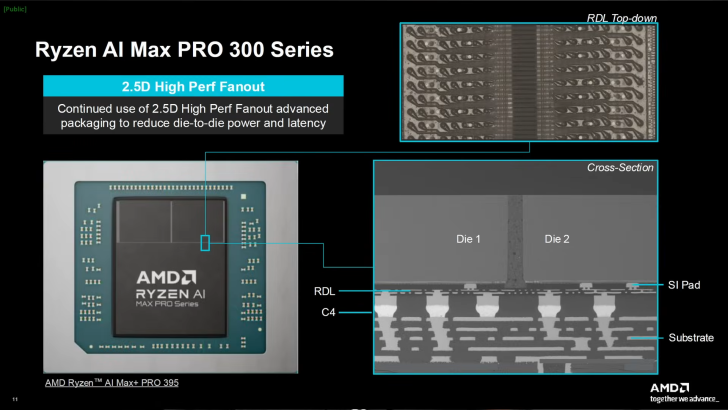

具体来说,AMD通过RDL(重分布层)在芯片间铺设了许多短而细的并行线缆,这些线缆位于芯片下方的“中介层”中。

通过台积电InFO-oS(集成扇出基板)技术,将线缆铺设在硅芯片和有机基板之间,使得CPU架构能够通过宽并行端口进行通信。

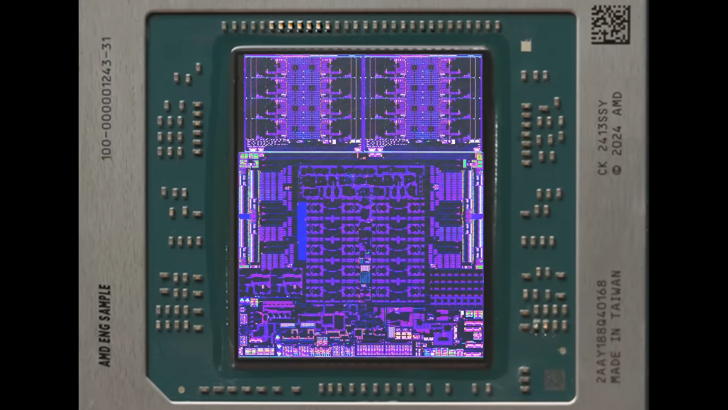

High Yield通过观察Strix Halo的芯片设计发现了这一新方法,Strix Halo的芯片上有一个矩形的小垫片区域,这是InFO-oS的经典表现形式,而原本的大“SERDES”模块已被移除。

这种新的D2D互连方式显著降低了功耗和延迟,因为不再需要串行化和解串行化过程,更重要的是,通过增加CPU架构中的端口数量,整体带宽得到了显著提升。

不过这种方法也带来了设计上的复杂性,尤其是在多层RDL的设计中,以及需要改变布线优先级,因为芯片下方的空间被用于扇出布线。