SK海力士、三星和美光加速16层堆叠HBM 都想供货给NVIDIA

存储三巨头SK海力士、三星和美光,正加速开发16-Hi HBM内存芯片,目标是在2026年第四季度向NVIDIA供货。据悉,NVIDIA已向供应商提出需求,希望在2026年第四季度正式交付16-Hi HBM芯片,用于其顶级AI加速器。

一位行业人士表示:“继12-Hi HBM4之后,英伟达又提出了16-Hi的供货需求,因此我们正在制定非常快速的开发时间表。性能评估最早可能在明年第三季度之前开始。”

16-Hi HBM技术尚未实现商业化,其开发面临诸多技术难题,尤其是随着堆叠层数的增加,DRAM堆叠的复杂性呈指数级上升。

根据JEDEC标准,HBM4的总厚度限制在775µm,要在这一有限空间内塞进16层DRAM芯片,意味着晶圆厚度必须从目前的50µm压缩至30µm左右,而如此薄的晶圆在加工中极易损坏。

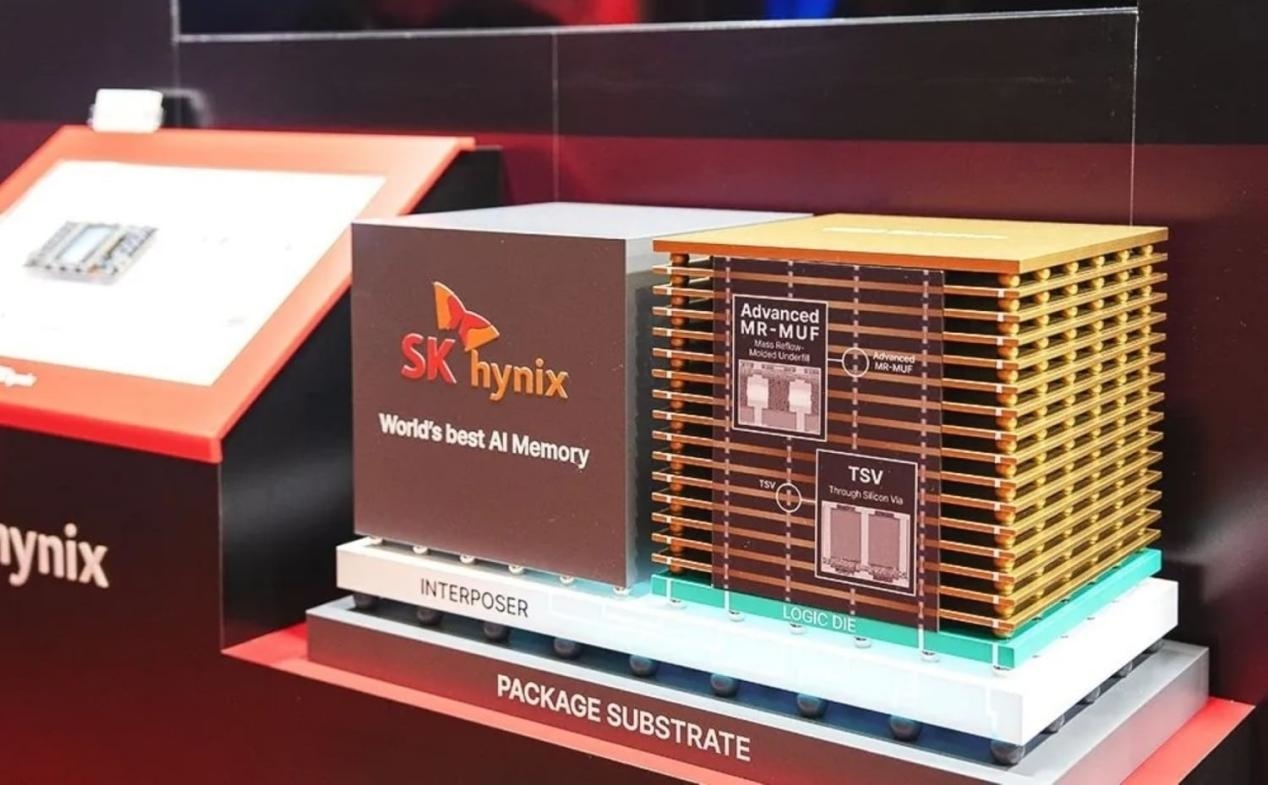

此外,粘合工艺也是竞争焦点,目前三星与美光主要采用 TC-NCF技术,而SK海力士则坚持MR-MUF工艺。

为了增加堆叠层数,粘合材料的厚度必须缩减到10µm以下,如何在极致轻薄化后依然能有效散热,是三家企业必须跨越的“大山”。

16-Hi被视为半导体行业的一道分水岭,根据行业蓝图,下一代HBM5的堆叠层数也仅能达到16层,预计到2035年的HBM7才会实现20层和24层堆叠,而未来的HBM8也将止步于24层堆叠。