原子级别的成像技术揭示计算机芯片内部存在"鼠咬"缺陷

美国康奈尔大学研究团队首次在原子尺度上直接“看见”了隐藏在先进芯片内部的结构缺陷,并将这些微小的不规则形态形象地称为“鼠咬”(mouse bites),这一成像突破为未来高端芯片的调试和良率提升提供了全新工具。

这项新技术依托一种高分辨率三维电子成像方法,由康奈尔大学与台积电(TSMC)及半导体设备厂商 ASM 合作开发,能够在纳米乃至原子尺度上重建晶体管内部结构,直接定位影响性能和可靠性的微观缺陷。 研究成果已于 2 月 23 日发表在《自然·通讯》(Nature Communications)期刊上,论文第一作者为康奈尔大学博士生 Shake Karapetyan。

项目负责人、康奈尔 Duffield 工程学院 Samuel B. Eckert 讲席教授 David Muller 表示,在现有手段中几乎不可能直接看到这些缺陷的原子结构,而新方法将成为芯片开发阶段进行“调试”和“故障排查”的关键表征工具。 由于从智能手机、汽车到人工智能数据中心和量子计算机都依赖先进芯片,这一进展有望在整个信息产业链条产生广泛影响。

在现代半导体器件中,晶体管是控制电流开关的核心单元,其沟道区域就像一根给电子“走路”的微型管道。 Muller 形容,如果这根“管道”的内壁很粗糙,就会阻碍电子流动,因此精确测量沟道壁的粗糙程度、分辨哪些区域“好”、哪些“坏”,在原子尺度下变得尤为关键。 如今高性能芯片里的晶体管沟道宽度只有大约 15 至 18 个原子,结构极其复杂,任何一点微小偏差都可能造成可测的性能差异。 Karapetyan 直言,在这样的尺寸下几乎“每一个原子的位置都很要紧”,而准确刻画这些结构一直是难题。

回顾半导体技术发展早期,晶体管大多以平面方式布局,在芯片表面横向展开。 随着尺寸不断逼近物理极限,业界转向三维堆叠结构,将器件垂直“竖起来”,形成日益复杂的 3D 架构。 Muller 回忆,自己在 1997 至 2003 年在贝尔实验室工作期间,就曾研究限定晶体管极限缩小尺寸的物理因素。 如今,这些 3D 结构的特征尺寸已经小于许多传统表征手段的分辨能力,诊断性能问题愈发困难。

先进电子显微技术的演进,为破解这一难题奠定了基础。 Muller 与现任 ASM 技术副总裁、康奈尔校友 Glen Wilk 在贝尔实验室期间,曾合作研究以高介电常数的氧化铪(HfO₂)替代在小尺寸下漏电严重的二氧化硅,作为栅极材料,这一工作后来推动了氧化铪在电脑和手机芯片中的普及应用。 当年他们发表的利用电子显微镜表征相关材料的论文,曾被半导体业内广泛研读。

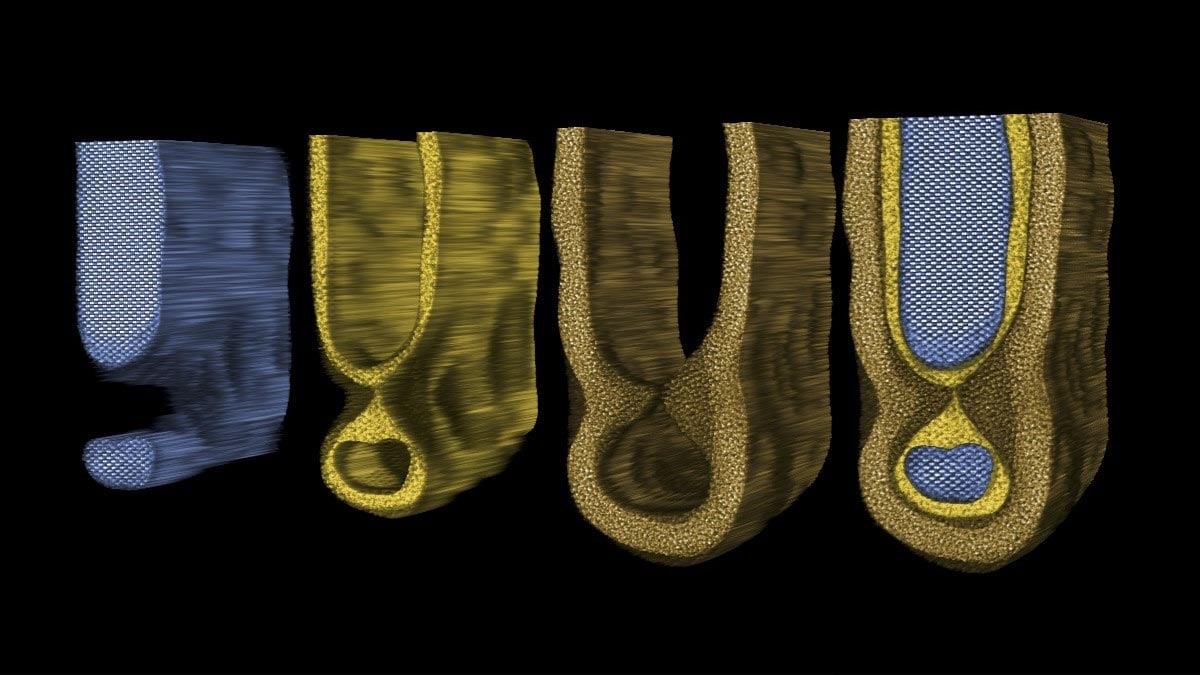

如今,Muller 口中的“螺旋桨飞机”已经升级为“喷气式战机”,具体体现便是电子正电子衍射成像(electron ptychography)技术。 该方法依赖一种由其课题组参与开发的电子显微像素阵列探测器(EMPAD),通过记录电子束穿过晶体管时产生的散射图样,再对相邻扫描点间图样的细微变化进行计算重构,从而获得超高分辨率图像。 EMPAD 的精度之高,曾被吉尼斯世界纪录认定为实现了迄今分辨率最高的原子级成像。

在台积电及其企业分析实验室、纳米电子研究中心 Imec 的支持下,Muller 与 Wilk 在 25 年后再度联手,将 EMPAD 技术应用到当代前沿半导体结构上。 Karapetyan 将这一过程比喻为解一道“超大拼图”,既要采集海量实验数据,又要完成复杂的计算重建。

通过对数据的处理与分析,团队得以追踪单个原子的空间位置,并量化晶体管沟道界面的细微起伏,他们将这些微小的凹坑和粗糙统称为“鼠咬”缺陷。 这些缺陷形成于器件制备过程中经过优化的材料生长步骤之中,而用于测试的样品则来自 Imec 的工艺线。 Karapetyan 指出,现代器件的制备往往要经历数百甚至上千道化学刻蚀、沉积与热处理步骤,每一步都会对最终结构产生影响,以往只能依靠投影成像“猜测”内部发生了什么,而现在则可在若干关键步骤后直接“看”到结构变化。 这使得工艺工程师有机会更精细地调节温度等工艺参数并实时验证其结构结果。

研究团队认为,这种直接可视化原子缺陷的能力,将对依赖先进芯片的几乎所有技术形态产生潜在影响,包括智能手机、笔记本电脑、大型数据中心等常规应用,以及对材料结构精度要求极高的下一代量子计算系统。 Karapetyan 表示,有了这样一套工具,未来无论在基础科学研究还是工艺工程控制上,都将有更大的发挥空间。